ADC - Add with Carry Adds two registers and the contents of the C flag and places the result in the destination register Rd. 0001 11rd dddd rrrr ADD - Add without Carry Adds two registers without the C flag and places the result in the destination register Rd. Rd ← Rd + Rr. 0000 11rd dddd rrrr ADIW - Add Immediate to Word Adds an immediate value (0-63) to a register pair and places the result in the register pair. This instruction operates on the upper four register pairs, and is well suited for operations on the pointer registers. This instruction is not available in all devices. Refer to the device specific instruction set summary. Rd+1:Rd ← Rd+1:Rd + K. 1001 0110 KKdd KKKK BRCC - Branch if Carry Cleared Conditional relative branch. Tests the Carry flag (C) and branches relatively to PC if C is cleared. If C = 0 then PC <- PC + k + 1, else PC <- PC + 1. 1111 01kk kkkk k000 BRNE - Branch if Not Equal. Conditional relative branch. Tests the Zero flag (Z) and branches relatively to PC if Z is cleared. If Rd ≠ Rr (Z = 0) then PC ← PC + k + 1, else PC ← PC + 1. 1111 01kk kkkk k001 CP- Compare. This instruction performs a compare between two registers Rd and Rr. None of the registers are changed. All conditional branches can be used after this instruction. CP Rd,Rr 0 ≤ d ≤ 31, 0 ≤ r ≤ 31 PC ← PC + 1. 0001 01rd dddd rrrr LD - Load Indirect from data space to Register using Index X. Loads one byte indirect from the data space to a register. LD Rd, X . 1001 000d dddd 1100 LDI - Load Immediate. Loads an 8 bit constant directly to register 16 to 31. LDI Rd,K. 1110 KKKK dddd KKKK

MOV - Copy Register. This instruction makes a copy of one register into another. The source register Rr is left unchanged, while the destination register Rd is loaded with a copy of Rr. MOV Rd,Rr. 0010 11rd dddd rrrr MUL- Multiply Unsigned. This instruction performs 8-bit  $\times$  8-bit  $\rightarrow$  16-bit unsigned multiplication. result placed in r1, r0 (HL). MUL Rd,Rr. 1001 11rd dddd rrrr

NEG- Two's Complement. Replaces the contents of register Rd with its two's complement; the value \$80 is left unchanged. NEG Rd. 1001 010d dddd 0001

SBC- Subtract with Carry. Subtracts two registers and subtracts with the C flag and places the result in the destination register Rd. SBC Rd,Rr. 0000 10rd dddd rrrr

ST - Store Indirect From Register to data space using Index X. Stores one byte indirect from a register to data space. ST X+, r26. (i) 1001 001r rrrr 1100

SUB- Subtract without Carry. Subtracts two registers and places the result in the destination register Rd. SUB Rd,Rr. 0001 10rd dddd rrrr

ICALL - Indirect Call to Subroutine. ndirect call of a subroutine pointed to by the Z (16 bits) pointer register in the register file. 1001 0101 0000 1001

IJMP - Indirect Jump. Indirect jump to the address pointed to by the Z (16 bits) pointer register in the register file.

LPM - Load Program Memory. Loads one byte pointed to by the Z register into the destination register Rd. LPM Rd, Z. 1001 000d dddd 0100

STA -(x);  $M(x) \leftarrow M(x)$ -1,  $M(M(x)) \leftarrow AC$ , Fetch Cycle Step 1: MAR ← PC; Step 2: MDR ← M(MAR), PC ← PC+1 Step 3: IR  $\leftarrow$  MDR opcode , MAR  $\leftarrow$  MDR address ; Read inst. & increment PC Execute Cycle

Step 1:  $MDR \leftarrow M(MAR)$ ; Get EA+1 from memory (i.e., M(x))

Step 2: TEMP ← AC ; Save AC to TEMP

Step 3: AC ← MDR; Decrement EA+1

Step 4: AC ← AC -1:

Step 5: MDR  $\leftarrow$  AC; Store EA into M(x)

Step 6: M(MAR) ← MDR; Step 7: AC ← TEMP ; Restore AC

Step 8: MAR ← MDR ; Have MAR point to EA

Step 9: MDR  $\leftarrow$  AC ; Store content of AC into M(M(x))=M(EA)

Step 10: M(MAR) ← MDR;

adiw ZH:ZL,32

Fetch cycle

Step 1: MAR ← PC;

Step 2: MDR ← M(MAR), PC ← PC+1; Get the high byte of the instruction and increment PC

Step 3: IR  $\leftarrow$  MDR ; At this point, CU knows this is adiw

Step 4: MAR ← PC:

Step 5: MDR ← M(MAR), PC ← PC+1 ; Get the low byte of the

instruction and increment PC

Execute cycle

Step 6: AC ← R30

Step 7: AC ← AC + MDR : Add 32 to ZL

Step 8: R30 ← AC ; Add 32 to ZL

Step 9: AC ← R31

Step 10: If (C==1) then AC ← AC +1; Increment ZH if there was a

Step 11: R31 ← AC ; Write it back to register file

ICAL I

: Fetch cycle Step 1: MAR ← PC:

Step 2: MDR ← M(MAR), PC ← PC+1; Get the high byte of the

instruction and increment PC

Step 3: IR(15...8) ← MDR

Step 4: MAR ← PC:

Step 5: MDR ← M(MAR), PC ← PC+1; Get the low byte of the

instruction and increment PC

Step 6: IR(7...0) ← MDR; At this point, CU knows this is an ICALL;

Execute cycle

; The return address is pushed onto the stack

Step 7: MDR  $\leftarrow$  PC(7...0) Step 8: MAR  $\leftarrow$  SP

Step 9: M(MAR) ← MDR, SP ← SP-1; Push the lower byte of return address onto stack

Step 10: MDR ← PC(15...8)

Step 11: MAR ← SP

Step 12:  $M(MAR) \leftarrow MDR$ ,  $SP \leftarrow SP-1$ ; Push the higher byte of

return address onto stack

: Put H and L target addresses of the Z register to the PC

Step 13: PC(15...8) ← R31; Put the H address of the target into PC

Step 14: PC(7...0) ← R30 ; Put the L address of the target into PC

Accumulator Indirect with Pre-Decrement" of the form STA -(x);  $M(x) \leftarrow M(x)$ -1,  $M(M(x)) \leftarrow AC$ , Suppose we want to implement this instruction on the pseudo-CPU discussed in class augmented with a temporary register TEMP. An instruction consists of 16 bits: A 4-bit operation code and a 12-bit address. All operands are 16 bits. PC and MAR each contain 12 bits. AC, MDR, and TEMP each contain 16 bits, and IR is 4 bits. Give the sequence of microoperations required to implement the Execute cycles for the above STA -(x) instruction. Your solution should result in minimum number of microoperations. Assume PC is currently pointing to the STA instruction and only PC and AC have the capability to increment/decrement itself. This instruction does not modify the original content of the AC. Fetch cycle is given below

Consider the following hypothetical 1-address assembly instruction called "Store

Things to remember:

Stack starts high and decrements as stuff is placed on it. Arithmetic: converting dec to binary: do you need x to get y? yes=1, no

Dec to Hex: divide number by 16 and that is high byte, low byte = original number - the closest you got.

Two's complement:

Two's complement is the way every computer I know of chooses to represent integers. To get the two's complement negative notation of an integer, you write out the number in binary. You then invert the digits, and add one to the result.

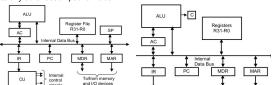

| Consider the internal structure of the pseudo-CPU discussed in class augmented with a single-port register file (i.e., only one register value can be read at a time) 32 8-bit registers (R31-R0) and a carry bit (C-bit), which is set/reset after each arithmetic operation. Suppose the pseudo-CPU can be used |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| to implement the AVR instruction adiw ZH:ZL,32 (Add immediate to word). adiw                                                                                                                                                                                                                                      |

| is a 16-bit instruction, where the upper byte represents the opcode and the lower                                                                                                                                                                                                                                 |

| byte represents an immediate value, i.e., " 32 " (do not worry about the fact                                                                                                                                                                                                                                     |

| that the actual format is slightly different). Give the sequence of microoperations                                                                                                                                                                                                                               |

| required to Fetch and Execute the adiw instruction. Your solutions should result                                                                                                                                                                                                                                  |

| in exactly 5 cycles for the fetch cycle and 6 cycles for the execute cycle. Assume                                                                                                                                                                                                                                |

| the memory is organized into addressable bytes (i.e., each memory word is a                                                                                                                                                                                                                                       |

| byte), MDR, IR, and AC registers are 8-bit wide, and PC and MAR registers are                                                                                                                                                                                                                                     |

| 16-bit wide. Also, assume Internal Data Bus is 16-bit wide and thus can handle                                                                                                                                                                                                                                    |

| 8-bit or 16-bit (as well as portion of 8-bit or 16-bit) transfers in one                                                                                                                                                                                                                                          |

| microoperation and only PC and AC have the capability to increment itself.                                                                                                                                                                                                                                        |

Consider the internal structure of the pseudo-CPU discussed in class augmented with a single-port register file (i.e., only one register value can be read at a time) containing 32 8-bit registers (R0-R31) and a Stack Pointer (SP). Suppose the pseudo-CPU can be used to implement the AVR instruction ICALL (Indirect Call to Subroutine) ICALL pushes the return address onto the stack and jumps to the 16-bit target address contained in the Z register. Give the sequence of microoperations required to Fetch and Execute AVR's ICALL instruction. Your solutions should result in exactly 6 cycles for the fetch cycle and 8 cycles for the execute cycle. Assume the memory is organized into addressable bytes (i.e., each memory word is a byte), MDR register is 8-bit wide, and SP, PC, IR, and MAR are 16-bit wide. Also, assume Internal Data Bus is 16-bit wide and thus can handle 8-bit or 16-bit (as well as portion of 8-bit or 16-bit) transfers in one microoperation and SP has the capability to increment/decrement itself. Clearly state any other assumptions made.

Assembler Directives

ORG: Tells the assembler where to put the instructions that follow

EXIT: Tells the assembler to stop assembling the file

EQU: Assigns a value to a label. Syntax: .EQU label = expression

.EQU io offset = 0x23

BYTE: Reserves memory in data memory

Syntax: label: .BYTE expression

var: .BYTE 1

DB: Allows arbitrary bytes to be placed in the code.

Syntax: label: .DB expressionlist

consts: .DB 0, 255, 0b01010101, -128, 0xaa Text: .DB "This is a text.

DW: Allows 16-bit words to be placed into the code

Syntax: label: .DW expressionlist

varlist: .DW 0,0xffff,0b1001110001010101,-32768,65535 INCLUDE: Tells the assembler to read from the specified file.

Syntax: .INCLUDE filename .INCLUDE "m128def.inc"

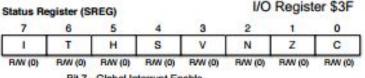

Bit 7 - Global Interrupt Enable

Bit 6 - Bit- Copy Storage

Bit 5 - Half Carry Flag

Bit 4 - Sign Bit Bit 3 - Two's Complement Overflow Flag

Bit 2 - Negative Flag

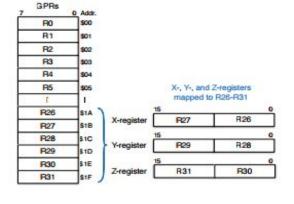

Bit 1 - Zero Flag Bit 0 - Carry Flag Consider the implementation of the CPI Rd,K Consider the implementation of the LD Rd,Y+ (Load Indirect and Post-Increment) (Compare Register with Immediate) instruction on instruction on the enhanced AVR datapath. the enhanced AVR datapath. (a) List and explain the sequence of microoperations required to implement LD Rd,Y+. - EX1: DMAR ¬ Yh:YL, Yh:Yl ¬ Yh:Yl + 1 EX2: Rd ¬ M[DMAR] (b) List and (a) List and explain the sequence of microoperations required to implement CPI Rd,K.

Control

MJ MK ML

IR en

PC\_en PCh\_en

PCl\_en NPC\_en

SP en DEMUX

MA

MB

ME

MF MG

DM 1

DM w

Adder f

Inc\_Dec MH

ALU 1

XXXX

RAL

Rd

EX: Rd - K

Control

Signals

MJ

MK ML

IR en PC\_en

PCh en PCl en NPC en

DEMUX MA

MB ALU\_f

MC

MD ME

MG

binaries on the

g address \$0049) saddress \$004B) ss \$005D) s \$005E)

nsider the AVR assembly co termine the values for KKKK ddda KKKK (@ add KKKK ddda KKKK (@ add Kk kKKK k (@ address \$0 KKda KKKK (@ address \$0 kkkk kkkk k(@ address \$0

e go e a g

RF\_wB

DM r DM\_w MF

Adder f

(b) List and explain the control signals and the

Register Address Logic (RAL) output for the CPI Rd,Kinstruction.

EX: The content of Rd is read from the Registe

overwritten in the fetch (i.e., next) cycle

EX

X

0

0010

XX

explain the control signals and the Register Address Logic (RAL) output for the LD Rd.Y+, Instruction. EX1: The contents of Yh and YI are read from the Register File by providing Yh and YI to rA and rB, respectively. Yh:YI or Y is routed to DMAR by setting MH to 0. At the cares" except RF\_wARF\_wB, DM\_w, IR\_en, and PC\_en (as well as PCh\_en and PCl\_en), which all need same time, Y is incremented by one by the Address Adder (via MUXG) by setting Adder\_f to 01, and then latched onto YH and YL (via MUXC) by setting both RF\_wA File by providing the register identifier Rd to rA. At and RF\_wB to 1's and providing Yh and Yl to wA and wB, respectively. All other the same time, the constant K from the instruction control signals can be don't cares except DM\_w, which needs to be set to 0 so that is routed (via the Alignment Unit) through MUXA the memory is not overwritten, and IR\_en, PC\_en, as well as PCh\_en and PCl\_en,

by setting MA to 0. The ALU then performs a and SP\_en, which are all set to 0's to prevent IR, PC\_en, as well as PCh\_en and PCl\_en, location by setting MA to 0. The ALU then performs a and SP\_en, which are all set to 0's to prevent IR, PC, and SP, respectively, from pointed to by SP, i.e., subtract operation (ALU\_f = 0010), which then sets being overwritten. The RAL output for rA and rB are set to Yh and YI, respectively, so address to the Data M the appropriate condition flags (e.g., C, Z, N, V, and that the upper and lower bytes of Y can be read from the register file. This is also the DEMUX to the upper S flags in SREG). Note that the result of the ALU case for wA and wB since updated value of Y needs to be written back. ubtract operation (ALU\_f = 0010), which then sets being overwritten. The RAL output for rA and rB are set to Yh and YI, respectively, so address to the Data Memory by setting ME to 0 and DM\_r to 1. The read value is then routed through operation does not have to be stored back into the EX2: The content of DMAR is routed through MUXE and used to fetch the operand register file. All other control signals can be don't from Data Memory. The fetched operand is routed through MUXB and MUXC to the prevent the

need to be set to 0's so that the memory and the be don't cares except DM w, which needs to be set to 0 so that the memory is not PCh\_en and PCl\_en) and SP\_en are set to 0's to to be set to 0 to prevent the PC register, the SP register, and the register file, prevent PC and SP from being overwritten. Note

that IR\_en can be "don't care" since this is the last the last execute cycle and the IR register will be overwritten in the fetch (i.e., next) (the only) execute cycle and the IR register will be cycle. The RAL output for wB has to be set to Rd because the loaded value from memory has to be written to the destination registe

Signals

MK

IR\_en

PC en

PCI en NPC en SP en

DEMUX

ALU f

RF wA

RF wB

ME

DM r

DM\_w MF

Adder\_f

Inc Dec

MG

XXXX

XX

MA

MB

XXXX

EX1

XXXX

XX

EX2

1

0

XXXX 01

0

LD Rd, Y-

0

0

XXXX

0

Consider the implementation of the RET (Return from Subroutine) instruction on the enhanced AVF datanath

(a) List and explain the sequence of microoperations required to implement RET. - EX1: SP ¬SP +1, EX2:

PCh - M[SP], SP - SP +1, EX3: PCI - M[SP]

(b) List and explain the control signals and the Register Address Logic (RAL) output for the RET instruction EX1: The content of SP is routed to the Increment/Decrement Unit, and incremented by setting Inc\_Dec to 0. The incremented SP is then relatched onto SP by setting SP\_en to 1. All other control signals can be "don't

to be set to 0's to prevent the register file, Data Memory, IR, and PC from being overwritten with unwanted EX2: The content of SP is routed to the Increment/Decrement Unit, and incremented by setting Inc\_Dec to 0. The incremented SP is then relatched onto SP by setting SP, en to 1. At the same time, the Data Memory

pointed to by SP, i.e., M[SP], which is the higher byte of the return address, is read by providing SP as an

byte of PC, i.e., PCh by setting DEMUX to 1 and PCh\_en to 1. All other control signals can be don't cares

except RF\_wA/RF\_wB, DM\_w, IR\_en, and PC\_en (as well as PCI\_en), which all need to be set to 0's to

cares except DM\_w, RF\_wA, and RF\_wB, which inB of the register file and written by setting RF\_wB to 1. All other control signals can register file, Data Memory, IR, and PC from being overwritten with unwanted values

EX3: The Data Memory location pointed to by SP, i.e., M[SP], which is the lower byte of the return address. register file are not updated, and PC\_en (as well as overwritten. PC\_en (as well as PCh\_en and PCl\_en), SP\_en, RF\_wA, which all needis read by providing SP as an address to the Data Memory by setting ME to 0 and DM\_r to 1. The read value is then routed to DEMUX to the lower byte of PC, i.e., PCI, by setting DEMUX to 0 and PCI\_en to 1.

respectively, from being overwritten. Note that IR\_en can be "don't care" since this is All other control signals can be don't cares except Sp\_en, RF\_wA/RF\_wB, DM\_w and PC\_en (as well as PCh\_en),, which all need to be set to 0's to prevent the SP, register file, Data Memory, and PC from being overwritten with unwanted values. Note that IR en can be "don't care" since this is the last execute cycle and IR register will be overwritten in the Fetch (i.e., next) cycle.

| Control | IF   |      | LPM  |     | -   | 2     | 4        | 4   |       | Control | ***  | RET  |      |      |  |  |  |  |  |

|---------|------|------|------|-----|-----|-------|----------|-----|-------|---------|------|------|------|------|--|--|--|--|--|

| Signals | II   | EX1  | EX2  | EX3 | _ = | 7     | 8        | 5   | RAL   | Signals | IF   | EX1  | EX2  | EX3  |  |  |  |  |  |

| MJ      | 0    | x    | x    | x   |     | П     |          | 3   | 1 1   | MJ      | 0    | X    | X    | X    |  |  |  |  |  |

| MK      | 0    | X    | x    | X   | 1   | Ц     | 4        | 1   |       | MK      | 0    | X    | X    | X    |  |  |  |  |  |

| ML      | 0    | X    | 1    | X   | -   |       |          |     |       | ML      | 0    | X    | X    | X    |  |  |  |  |  |

| IR en   | 1    | 0    | 0    | X   |     | ×     | ×        | ×   |       |         | 1    | A .  | 0    | _    |  |  |  |  |  |

| PC en   | 1    | 0    | 0    | 0   |     |       |          | 1   | -     | IR en   | 1    | U    |      | X    |  |  |  |  |  |

| PCh_en  | 0    | 0    | 0    | 0   | L   | Ц     | _        | 4   | - 1   | PC_en   | 1    | 0    | 0    | 0    |  |  |  |  |  |

| PCI_en  | 0    | .0   | 0    | 0   |     | П     |          | П   |       | PCh en  | 0    | 0    | 1 1  | 0    |  |  |  |  |  |

| NPC en  | 1    | X    | X    | X   | 2   | ×     |          | ×   | R     | PCl en  | 0    | 0    | 0    | 1    |  |  |  |  |  |

| SP en   | 0    | 0    | 0    | 0   |     |       |          | i   | 3     | NPC en  | 1    | x    | x    | X    |  |  |  |  |  |

| DEMUX   | X    | X    | x    | X   | 1   |       | 4        | 41  | SP en | 0       | 1    | 1    | 0    |      |  |  |  |  |  |

| MA      | X    | X    | X    | X   | 1   | П     |          | I.  |       | DEMUX   | x    | X    | 1    | 0    |  |  |  |  |  |

| MB      | X    | X    | X    | X   | ×   | ×     | ×        | ×   | 2     |         |      | _    |      | _    |  |  |  |  |  |

| ALU_f   | XXXX | XXXX | XXXX | XXX |     | П     |          | 1   | **    | MA      | X    | X    | X    | X    |  |  |  |  |  |

| MC      | XX   | XX   | XX   | 10  | L   | Ш     |          | _   | ш     | MB      | X    | X    | X    | X    |  |  |  |  |  |

| RF_wA   | 0    | 0    | 0    | 0   | 3   | TA NO | 5 3      | =   | -     | ALU f   | XXXX | XXXX | XXXX | XXXX |  |  |  |  |  |

| RF_wB   | 0    | 0    | 0    | 1   | ]~[ | 7     | 2        | 2 8 | RAL   | MC      | XX   | XX   | XX   | XX   |  |  |  |  |  |

| MD      | x    | x    | x    | X   |     |       | wA<br>wB | p   | F     | RF wA   | 0    | 0    | 0    | 0    |  |  |  |  |  |

| ME      | X    | X    | X    | X   |     |       |          |     | RF wB | 0       | 0    | 0    | .0   |      |  |  |  |  |  |

| DM r    | x    | x    | x    | x   |     |       | Т        | Т   | T     | MD      | X    | X    | X    | X    |  |  |  |  |  |

| DM_w    | 0    | 0    | 0    | 0   | N   | Zh    | ٦,       | . 2 | 9 1   | ME      |      |      | 0    | 0    |  |  |  |  |  |

| MF      | X    | X    | X    | X   | 1-1 | 3     | 1        | 12  | 4     |         | X    | X    | 6    | 0    |  |  |  |  |  |

| MG      | ×    | 1    | · v  | v   | 7 1 |       | ш.       |     | -1-1  | DM r    | X    | X    |      |      |  |  |  |  |  |

MF

MI

Inc\_Dec MH

## MI MI Consider the implementation of the RCALL (Relative Call to Subroutine) instruction on the enhanced AVR datapath

(a) List and explain the sequence of microoperations required to implement RCALL. - EX1: M[SP] ← RARI, SP ← SP - 1 EX2: M[SP] ← RARh, SP ← SP - 1, PC ← NPC + se k

(b) List and explain the control signals and the Register Address Logic (RAL) output for the RCALL instruction EX1: SP provides the address for the Data Memory by setting ME to 0, and then RARI is written to the Data Memory by setting MI to 0, MD to 0 and DM\_w to 1. At the same time, SP is decremented using the Increment/Decrement Unit by setting Inc\_Dec to 1 and latched onto the SP by setting SP\_en to 1. All other control signals can be "don't cares" except IR en and NPC en, which need to be set to 0's to prevent the IR register and the NPC register (as well as RAR) from being overwritten. Note that PC\_en can be don't care since PC will be overwritten in EX2. Finally, RAL output can be all don't cares because the register file is not used.

EX2: SP provides the address for the Data Memory by setting ME to 0, and then RARh is written to the Data Memory by setting MI to 1, MD to 0 and DM\_w to 1. At the same time, SP is decremented using the Increment/Decrement Unit by setting Inc\_Dec to 1 and latched on to the SP by setting SP\_en to 1. In addition, NPC and se K are added using the Address Adder by setting MG to 0, MF to 0, and Adder\_f to 00. The resulting target address is latched onto the PC by setting MJ to 1and PC\_en to 1. All other control signals can be don't cares. Note that IR\_en can be "don't care" since this is the last execute cycle and the IR register will be overwritten in the fetch (i.e., next) cycle. Also, NPC\_en can be "don't care" because the content of RAR (as well as NPC) will not change until the end of the cycle, so there is no danger of the return address in RAR being modified while the RARh is pushed onto the stack, and will be updated by the fetching of the has to be set to Rd (which happens to be 0) because the loaded value from memory has to be written to a destination instruction from the

(a) List and explain the sequence of microoperations required to implement LPM, - EX1; PMAR ← Zh;ZI EX2; MDR ← M[PMAR] EX3: R0 ← MDR

Consider the implementation of the LPM (Load Program Memory) instruction on the enhanced AVR datapath

(b) List and explain the control signals and the Register Address Logic (RAL) output for the LPM instruction. EX1: The Zh and ZI registers are read from the Register File by providing Zh and ZI to rA and rB, respectively. Zh:ZI \ is then latched onto the PMAR register. This is done by routing through the Address Adder by setting MG to 1 and Adder\_f to 11. All other control signals can be "don't cares" except RF\_wA and RF\_wB to prevent the register file from being updated. In addition, IR\_en, DM\_w, PC\_en, and SP\_en need to be set to 0's to prevent IR register, Data Memory, PC register, and SP register, respectively, from being overwritten. The RAL output for rA and rB are set to Zh and ZI, respectively, so that the upper and lower bytes of Z can be read from the register file. EX2: The Program Memory is read based on PMAR by setting ML to 1, and then the value read is latched onto MDR. All

other control signals can be don't cares except RF\_wA/RF\_wB, IR\_en, DM\_w, PC\_en, and SP\_en, which need to be set to 0's to prevent the register file, IR register, Data Memory, PC register, and SP register, respectively, from being overwritten. Finally, RAL output can be all don't cares because the register file is not used. EX3: The content of MDR is written back to R0 in the register file by setting MC to 10, rB to 00000002, and RF\_wB to 1. All other control signals can be don't cares except DM\_w, PC\_en, and SP\_en, which need to be set to 0's to prevent Data

Memory, PC register, and SP register, respectively, from being overwritten. Note that IR\_en can be "don't care" since this is the last execute cycle and the IR register will be overwritten in the Fetch (i.e., next) cycle. The RAL output for wB

| he ta               | rget      | anyv           | vay.           | Fina  | ally,          | RA        | Lo   | utp    | ıt c  | an    | be   | all   | dor         | 't c  | care    | es l               | ec      | aus      | e tt       | ne re          | gister           | file |              |                                                                                |      |                         |                                                                                                |                                                | register                           |                       |                                       |                                   |                                   |                                                                                 |                           |                          |           |                                    |         |                      |                   |           |           | 200,000                        |

|---------------------|-----------|----------------|----------------|-------|----------------|-----------|------|--------|-------|-------|------|-------|-------------|-------|---------|--------------------|---------|----------|------------|----------------|------------------|------|--------------|--------------------------------------------------------------------------------|------|-------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|-----------------------|---------------------------------------|-----------------------------------|-----------------------------------|---------------------------------------------------------------------------------|---------------------------|--------------------------|-----------|------------------------------------|---------|----------------------|-------------------|-----------|-----------|--------------------------------|

|                     |           |                |                |       |                |           |      |        |       |       |      |       |             |       |         |                    |         |          |            |                |                  |      | SS           | 4 1                                                                            |      |                         | -                                                                                              | 6                                              | 3 .:                               |                       |                                       | BIT-T                             | _                                 | INSTRUCT                                                                        | $\overline{}$             |                          |           |                                    |         | _                    |                   |           |           |                                |

|                     |           | ~ ~            | ~ ~            |       |                | · -       | -    | · -    | _     |       |      |       | 0.0         |       | ~       | -                  | ~       | ~ -      |            |                |                  |      | dre          | 0.0                                                                            |      | 5                       | ز                                                                                              | =                                              | ore                                |                       | LSL                                   |                                   | R                                 | d                                                                               | Lo                        | ogical Shift             | Left      |                                    |         | Rd(r                 | (n+1) ←           | Rd(n),Rd  | (0) ← 0,C | ← Rd(7)                        |

|                     |           | XX             | KK             | KKKK  | X              | KKKK      | 00   | 100    | 00    | 8     | 00   | E     | 000         | 010   | X       | 000                | KK      | KK       | k001       | X              |                  |      | ad ad        | is \$0104.                                                                     |      |                         | ē.                                                                                             | 9                                              | Therefore,                         |                       | LSR                                   |                                   | R                                 | d                                                                               | Lo                        | ogical Shift             | Right     |                                    |         | Rd(r                 | (n) ← Ro          | d(n+1),Rd | (7) ← 0,C | ← Rd(0)                        |

|                     |           | XX             | ××             | i M h | S M            | × -       | -    | HC     | 0     | H 1   | 0    | H     | 00          | 0     | ×       | 4 4                | ×       | × -      | * ×        | ×              |                  |      | JOI          | dddd                                                                           |      |                         | 010                                                                                            | 80                                             | g =                                |                       | ROL                                   |                                   | R                                 | đ                                                                               | R                         | otate Left T             | hrough    | h Carry                            |         | Rd(                  | (0) ← C,          | Rd(n+1)   | ← Rd(n),C | ← Rd(7)                        |

| KKKK                | i.        | PP             | DI             | יקי   | g              | PI        | P    | D T    | P     | ם ז   | g    | P     | 0 7         | P     | P       | D 4                | P       | T T      | 3          | 3              |                  |      | Data Memory  |                                                                                |      | KK = 0000 0001 0010     | le l                                                                                           | 9                                              | 63                                 |                       | ROR                                   |                                   | R                                 | 1                                                                               | R                         | otate Right              | Throug    | gh Carry                           |         | Rd(                  | (7) ← C.          | Rd(n) ←   | Rd(n+1),C | ← Rd(0)                        |

| ×                   | н         | dddd           | dddd           | ğ     | ğ              | ddddd     | dd.  | ğ      | dd    | ğ     | ğ    | ddc   | ğ           | pp    | KK      | ğ                  | XX      | KK       | kkk        | 8              |                  |      | ta           | KK                                                                             |      | 0                       | ć                                                                                              | 5                                              | \$0063.                            |                       | ASR                                   |                                   | R                                 | 1                                                                               | A                         | rithmetic Sh             | rift Righ | ht                                 |         | Rd(r                 | (n) ← R           | d(n+1), n | 06        |                                |

| ıž                  | pp        |                |                |       |                |           |      |        |       |       |      |       |             |       |         |                    |         |          |            |                |                  |      | Da           | dictates that LA                                                               |      | 000                     | 8                                                                                              | 9                                              | at 5                               |                       | SWAP                                  |                                   | Ro                                | đ                                                                               | S                         | wap Nibbles              | s         |                                    |         | Rd(                  | (30) ↔            | Rd(74)    |           |                                |

| KK)                 | pppp      | XX             | XX             | KKKK  | KKKK           | KKKK      | POG  | P      | P000  | 7 7   | PO   | Fd    | ין ק        | 19    | 10      | 0 4                | =       | 13       | 01kk       | KK             |                  |      | .=           | 9.0                                                                            | 1    | 0                       | 2                                                                                              | 7                                              | 00001<br>l is at                   |                       | BSET                                  |                                   | 8                                 |                                                                                 | FI                        | ag Set                   |           |                                    |         | SRE                  | EG(s) ←           | - 1       |           | -                              |

| ILY                 | 1         | 22             | 2 5            | 2 5   | 2 2            | 2 6       | ö    | - 6    | 0     | 7 7   | 0    | 7     | 0 0         | 0     | 0       | 0 0                | 0       | 0 0      | 0          | 2              |                  |      | nory in I    | lict                                                                           |      | 00                      | 2                                                                                              | ) 90                                           | 3 = 5                              |                       | BCLR                                  |                                   | 8                                 |                                                                                 | FI                        | ag Clear                 |           |                                    |         | SRE                  | EG(s) ←           | - 0       |           |                                |

| Binary<br>kkkk kkkk | 01rd      | 00             | 00             | 000   | 0              | 0 -       | 0    |        | -     | 0 -   | . 0  | 1     | 0 -         |       | -       | -                  | -       |          |            | 0              |                  |      |              |                                                                                |      | 0 =                     | ď                                                                                              | 1                                              | 0011<br>8. PC+                     |                       | SBI                                   |                                   | P,                                | b                                                                               | Se                        | et Bit in I/O            | Regist    | ter                                |         | 1/0(                 | (P, b) ←          | 1         |           |                                |

|                     | 0         | 1110           | ==             | =     | =              | 118       | 8    | 000    | 00    | 000   | 00   | 000   | 000         | 00    | 00      | 111                | 00      | 000      | 11 8       | 110            |                  |      |              |                                                                                |      | X                       | ă,                                                                                             | 5                                              | thun th                            |                       | СВІ                                   |                                   | P,                                | b                                                                               | CI                        | lear Bit in I/           | O Reg     | ister                              |         | 1/0(                 | (P, b) ←          | 0         |           |                                |

| 1100                | 0010      |                | -              |       |                |           |      |        |       |       | , ,, |       | -           |       |         |                    | -       |          |            |                |                  |      | a byte of    |                                                                                |      | KKKK                    | MUL16_                                                                                         | 0                                              | KKKK<br>0062, t                    |                       | BST                                   |                                   | R                                 | r, b                                                                            | В                         | t Store from             | n Regis   | ster to T                          |         | T←                   | - Rr(b)           |           |           | -                              |

| =                   | 00        |                |                |       |                |           |      |        |       |       |      |       |             |       |         |                    |         |          |            |                |                  |      |              | drB: .b                                                                        |      | pppp                    | 10.                                                                                            | 7                                              | 3 × 8                              |                       | BLD                                   |                                   | R                                 | d, b                                                                            | В                         | t load from              | T to R    | tegister                           |         | Rd(                  | (b) ← T           |           |           |                                |

| Address<br>0000:    | 0046:     | 0047:          | 0049           | 0048  | 0040           | 004E      | 0020 | 0051   | 0053  | 0054  | 0056 | 0057  | 8500        | 005A  | 005B    | 00500              | 00 SE   | 005F     | 0001       | 0062           |                  |      | -            | . byte 2 and addrB:<br>of address LAddrP, which                                |      | thus KKKK d             | Hr, and brne                                                                                   | mairs is r25:r24 (dd=00) 27:r75 (dd=10)        | Therefore, KKdd KKKK = 0011 0001   |                       | .def<br>.def<br>.ORG<br>START<br>.ORG | sount<br>\$0000<br>: RJ<br>\$0002 | MP<br>2                           | r17                                                                             |                           |                          |           | ; Mult:<br>; Assur                 |         |                      |                   |           |           |                                |

| \$0000              | 946       | YL, low(addrB) | L, low(LAddrp) | 17, 2 | H, high(addrA) | r18, 2    | 4, Y | 3,14   | 4, 2+ | 0, r3 | 3, 2 | 3, r2 | - 0         | Z, r0 | H:ZL, 1 | 18<br>III.16 TLOOP | H:ZL, 1 | YH:YL, 1 | UL16_OLOOP | Done<br>\$0100 |                  |      | The          | . ORG \$0100 followed by addra: .byt. low(LAddrP) represents low byte of addre |      | imediate value is \$02, | is - 005E <sub>16</sub> = -000F <sub>16</sub> = -0001111 <sub>2</sub> = 1110001 <sub>2</sub> . | 1000 1<br>on upper four register pair          | fiate value is 1. e is \$0062, and | . 1111 1111 1111 1111 | INIT:                                 | LD<br>ST<br>LD<br>OU<br>LD        | I<br>S<br>I<br>T<br>I<br>RA,<br>I | mpr, 0h<br>EICRA,<br>mpr, 0h<br>EIMSK,<br>mpr, \$0<br>mpr<br>XH, hig<br>XL, low | mp:<br>b000<br>mp:<br>000 | r<br>000001<br>r<br>CTR) |           | ; to de<br>; Enab;<br>;<br>; Set 1 | les int | n in<br>erru<br>Dire | nterru<br>ipt for | or pin    | a risi    | n INTO<br>ing edge<br>or input |

| SOC                 | \$0<br>r2 | HH             | NN             | 1 4 5 | ×              | 4 1       | н    | 4 1    | н     | 4 1   | 4 4  | н     | 13          | 1     | 2       | 4 2                | 2       | H 1      | ×          |                |                  |      | -            | low                                                                            |      |                         | 8                                                                                              | 1000                                           | mp mp                              |                       |                                       | LD                                |                                   | YH, hig                                                                         |                           |                          |           |                                    |         |                      |                   |           |           |                                |

| .org                |           | 141            | 141            |       |                | 1di       |      | Inm 19 | 14    | add   | 1d   | adc   | 8<br>+<br>+ | st    | adiw    | dec                | sbiw    | adiw     | brne       | rjmp.          | .byte            |      | risr         | \$ \$0100 fol                                                                  | 0100 | 1 0001 and the          | 004F                                                                                           | kkkk k = 11                                    | (dd=11). Th                        | CK KKK KKK            | WAIT:<br>.ORG<br>ISR:                 |                                   | MP<br>100                         | YL, low<br>WAIT<br>F<br>mpr, Pl<br>Y+, mpr<br>count                             | INA                       | ATA)                     |           |                                    |         |                      |                   |           |           |                                |

|                     | INIT:     | MAIN:          |                | 20010 | 9              | OTT ALTIN | 1    |        |       |       |      |       |             |       |         |                    |         |          |            | Done:          | addrA:<br>addrB: |      | The ZL is re | Space. ORG                                                                     |      | rd = r17 = 1            | at \$005E. T                                                                                   | Thus, kk kkkk k = 11<br>sbiw instruction works | and r31:r30 The target ac          | Thus, kkkk            | .DSEG<br>CTR:<br>DATA:                | RE'                               | T<br>YTE                          | X, cour                                                                         | int                       |                          |           |                                    |         |                      |                   |           |           |                                |

```

Write an AVR assembly code that waits for 1 sec using the

8-bit Timer/Counter0 with the system clock

frequency of 16 MHz operating under Normal mode. This is

```

done by doing the following: (1) Timer/Counter0 is initialized to count for 10 ms and then

interrupts on an overflow: (2) The main part of the program simply loops, and for each

iteration, a check is made to see if the loop has reach 100 iterations; and

(3) On each interrupt, Timer/Counter0 is reloaded to interrupt again in 10 ms.

The first thing that needs to be done is to calculate the value to be loaded onto Timer/Counter1. This is done by evaluating the following equation: value = 255 - (10 ms/( prescale x 62.5 ns)) = 255 - (16,000,000/prescale) We want to use a prescale value that would lead to the highest resolution (i.e., lowest prescale value) and yet satisfy the above equation, thus prescale = 1024. This leads to value = 99. Obviously, there are many ways to write this code, but here is one possibility: .include "m128def.inc"

```

.def mpr = r16

.def counter = r17

.ORG $0000

RJMP Initialize

.ORG $0020 ; Timer/Counter0 overflow interrupt OUT EIMSK, mpr ;

RCALL Reload counter

RETI

.ORG $0046 ; End of interrupt vectors

Initialize:

LDI mpr, 0b00000100 ; Enable interrupt on

Timer/Counter0 overflow

OUT TIMSK, mpr

SEI ; Enable global interrupt

LDI mpr, 0b00000111 ; Set prescalar to 1024

OUT TCCR0, mpr;

LDI mpr, 99 ; Load the value for delay

OUT TCNTO, mpr;

LDI counter, 100 ; Set timer

LOOP:

CPI counter, 0 ; Repeat for 100 times

BRNE LOOP

```

POP mpr RET The initialization part of the code first enables Timer/Counter0 overflow interrupt and the global interrupt. Then, the prescalar is set to 1024, i.e., CS02 = 1, CS01 = 1, and CS00 = 1. Note that the Normal mode of operation does not have to be explicitly configured since the Waveform Generation Mode bits are all 0s at reset, i.e., WGM13-10 = 0000 (Normal mode). The next part sets the Timer/Counter0 to value = 99. Once the Timer/Counter0 is set, the program enters a loop waiting for a Timer/Counter0 overflow interrupt to occur. In addition, counter is checked to see if it has reached zero. Finally, the Reload counter routine decrements the counter, reloads the value, and returns.

OUT TCNT0, mpr ; Load the value for delay

Consider the AVR code segment shown below that initializes and handles interrupts. Descriptions of Data Directional Register (DDRx), External Interrupt Control Registers (EICRA & EICRB), and External Interrupt Mask Register (EIMSK) are given on the following page. (a) Explain in words what the code accomplishes when it is executed. That is, explain what it does and how it does it, - This code reads an 8-bit value latched on to Port A when an interrupt occurs from INTO. It then stores it to memory starting at address DATA then increments a count, which will be stored in memory location at CTR.

(b) Write and explain the interrupt initialization code (lines (1)-(7)) necessary to make the interrupt service routine (starting at ISR:) work properly. More specifically.

```

.include "m128def.inc

.def mpr = r16 ; Multi-purpose register

.def count = r17; Assume R17 is initially 0

.ORG $0000

START - RIMP INIT

.ORG $0002

RCALL ISR

RETI

INIT: LDI mpr, 0b00000011; Sets Input Sense Control

for pin INTO

STS EICRA, mpr ; to detect an interrupt on a rising

edae

```

LDI mor, 0b00000001; Enables interrupt for pin INTO OUT DDRA, mpr ;

SEI ; Turn on interrupts LDI XH, high (CTR) LDI XL, low(CTR) LDI YH, high (DATA)

LDI YL, low(DATA) WAIT: RJMP WAIT .ORG 0x100F ISR: IN mpr, PINA ST Y+, mpr

INC count ST X, count RET .DSEG

CTR: .BYTE 1 DATA: .BYTE 256

Write a subroutine initUSART1 to configure ATmega128 USART1 to operate as a transmitter and sends a data every time USART1 Data Register Empty interrupt occurs The transmitter operates with he following settings: 8 data bits, 2 stop bits, and even parity 9,600 Baud rate, Transmitter enabled, Normal asynchronous mode operation, Interrupt enabled. Assume the system clock is 16 MHz. The skeleton code is shown below: There are many ways to write this code but here is one possible code for initUSART1. initUSART1:

```

Port D set up - pin3 output

ldi mpr, Ob00001000 ; Configure USART1 (Port D, pin 3)

out DDRD, mpr ; Set pin direction to output

; Set Baud rate

ldi mor, 103; Set baud rate to 9,600 with f = 16 MHz

sts UBRR1L, mpr ; UBRR1H already initialized to $00

; Enable transmitter and interrupt

ldi mpr, (1<<TXEN1|1<<UDRIE1) ; Enable Transmitter and interrupt

sts UCSR1B, mpr

; Set asynchronous mode and frame format

ldi mpr. (1<<USBS1|1<<UPM11|1<<UCSZ11|1<<UCSZ10)

sts UCSR1C, mpr; UCSR1C in extended I/O space, use sts

```

The first two instructions configure Pin 3, Port D for output since the USART1 is acting as a transmitter. The next two instructions set the Baud rate. This is done by calculating the UBRR value, which is (16MHz/(16x9600))-1 = 103, and then writing it into the UBRR1L register. The UBRR1H register was not written to since upper byte is \$00. The next two instructions enable the transmitter and the interrupt, which is done by setting the 3rd-bit (i.e., TXEN1) and the 5th-bit (i.e., UDRIE1) of UCSR1B. The next pair of instructions sets it LDI mpr, \$00; Set Port A Direction Register for input to the asynchronous mode, which is done by setting the 6th bit (i.e., UMSEL1) of UCSR1C to 0. Note that 0<<UMSEL1 is not necessary since it is already initialized to 0 on reset. This is also the case for 0<<UCSZ12 and 0<<UPM10. The frame format with 8 data bits, 2 stop bits, and even parity is set by selecting UCSZ12:0 to be 011, UPM11:0 to be 10, and USBS1 to 1. These bits are configured using

(1<<USBS1|1<<UPM11|0<<UPM10|0<<UCSZ12|1<<UCSZ11|1<<UCSZ10) Also note that sts is used because UCSR1C is in the extended I/O space. Here is a possible code for SendData, which is called when USART1 Data Register Empty interrupt occurs. SendData:

ld r17, X+: Assume X points to the data to be transmitted sts UDR1, r17; Move data to Transmit Data Buffer

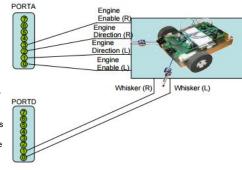

Consider the AVR code segment shown below that initializes I/O and interrupts for Tekbot shown below.

```

.include "m128def.inc"

.def mpr = r16

.org $0000

rjmp INIT

INIT: ldi mpr, Ob00001111 (1); Set DDRA to control engine

out DDRA, mpr (2);

ldi mpr, Ob00000000 (3); Set DDRD to detect whiskers

out DDRD, mpr (4)

ldi mpr, 0b00000011 (5); Enable pull-up resisters for L/R whiskers

out PORTD, mpr (6);

ldi mpr, 0b00001010 (7); Set EICR to detect on falling edge

sts EICRA, mpr (8) ;

ldi mpr, 0b00000011 (9); Set EIMSK

out EIMSK, mpr (10);

sei ; Turn on interrupts

```

; Pop the lower byte of return address from the stack

these contents are modified (in hexadecimal) after executing each of the following AVR assembly instructions. Do not be concerned about what happens to the Status Register (SREG) after the operation. Instructions are unrelated.

```

(i) sbiw

XH:XL, 2

(ii) ldi

r27, 85

(iii) ror

r2

(iv) adc

r2, r1

(v) sts

$0007, r28

```

Reload counter:

LDI mpr, 16;

DEC counter

PUSH mpr

## Solution:

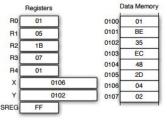

- Since X is \$0106, subtracting 2 results in \$0104. Thus, X changes to \$0104.

step8:AC<-AC+MDR

- (ii) R27 changes to \$55<sub>16</sub>. Thus, X changes to \$506<sub>16</sub> (iii) R2 is 00011011<sub>2</sub>, thus rotating it right through the carry, which is 1, results in 10001101<sub>2</sub>=8D<sub>16</sub>. Thus, R2 changes to \$8D. (iv) Status Register (SREG) indicates FF, thus C-bit (LSB) is set.

- Thus,  $1B_{16} + 05_{16} + 01(carry) = 21_{16}$ R2 changes to \$21

- (v) Since R28 is lower byte of Y registers, r28 = \$02, and thus M[0007]=\$02.

```

ADD - (x) M(x) < -M(x) -1, AC < -AC + (M(M(x)))

step1:MDR<-M(MAR), TEMP<-AC

step2:AC<-MDR

step3:AC<-AC-1

step4:MDR<-AC

step5:M(MAR)<-MDR

step6:MAR<-MDR

step7:MDR<-M(MAR), AC<-TEMP

```

Step 8: MAR ← SP

Step 11: MAR ← SP

Step 9:  $MDR \leftarrow M(MAR)$ ,  $SP \leftarrow SP+1$

Step 10:  $PC(15...8) \leftarrow MDR$

Step 12: MDR ← M(MAR),

Step 13:  $PC(7...0) \leftarrow MDR$

Goto fetch and Execute cycle

Based on the initial register and data memory contents shown below (represented in hexadecimal), show how Consider the internal structure of the pseudo-CPU discussed in class augmented with with a single-port register file (i.e., only one register value can be read at a time) containing 32 8-bit registers (R0-R31) and a Stack Pointer (SP) register. Suppose the very simple CPU can be used to implement the AVR instruction RET (Return from Subroutine) with the format shown below:

Step 1: MAR ← PC;

Step 2: MDR ← M(MAR), PC ← PC+1 ; Get the high byte of the instruction and increment PC

Step 3: IR(15...8) ← MDR Step 4: MAR ← PC;

Step 5: MDR  $\leftarrow$  M(MAR), PC  $\leftarrow$  PC+1 ; Get the low byte of the instruction and increment PC

Step 6:  $IR(7...0) \leftarrow MDR$ ; At this point, CU knows this is RET

Step 7: SP ← SP+1

; Pop the higher byte of return address from the stack